For decades, silicon defined the boundaries of power electronics performance. Today, Gallium Nitride (GaN) power devices are pushing beyond those limits. With higher breakdown strength, faster switching speeds, and dramatically lower switching losses, GaN power devices use smaller magnetics, higher efficiency, and greater power density across everything from USB-C chargers to EV drivetrains.

How GaN Power Devices Work — and Why They’re Replacing Silicon

Silicon has dominated power electronics for the past 5 decades. GaN is now displacing it. Not incrementally, but structurally.

Gallium Nitride (GaN) is a wide-bandgap (WBG) semiconductor that operates on fundamentally different principles than a conventional silicon MOSFET. Instead of relying on a doped channel, a GaN High Electron Mobility Transistor (HEMT) exploits a heterojunction — typically Aluminum Gallium Nitride (AlGaN) grown on a GaN layer. Spontaneous and piezoelectric polarization at this AlGaN/GaN interface creates a two-dimensional electron gas (2DEG) with high mobility and a large channel density, without the need for doping. That undoped, high-density electron channel is what gives GaN its edge: the 2DEG offers electron mobility of up to 2000 cm²/V·s — twice that of state-of-the-art silicon devices.

There’s a catch. A native GaN HEMT is a depletion-mode (d-mode) device, meaning it conducts at zero gate voltage, a fail-unsafe condition for power electronics. Manufacturers use two architectures to achieve the normally-off behavior that power systems require:

- Enhancement-mode (e-mode) GaN uses a p-GaN gate structure to shift the threshold voltage positive, creating a normally-off device. The threshold voltage VGS(th) is very low — typically 1 to 2 V — making the device sensitive to unintended switch-on in high dv/dt applications, which makes gate driver design demanding.

- Cascode GaN co-packages a high-voltage d-mode GaN HEMT with a low-voltage silicon MOSFET to achieve enhancement-mode operation. This interface naturally isolates the device gate, offering an automotive-grade maximum gate rating of ±20 V, with exceptional reliability and a high drive margin.

Neither approach is universally superior. E-mode devices offer a smaller footprint and tighter integration; cascode devices preserve the 2DEG in its natural, unmodified state and tolerate the same gate drive signals as a standard silicon MOSFET.

GaN vs. Silicon: Key Characteristics Compared

The performance gap between GaN and silicon ultimately traces back to one fundamental parameter: bandgap energy.

GaN vs. Silicon Bandgap

GaN has a wide bandgap of 3.4 eV, compared to silicon’s 1.12 eV, and a critical breakdown electric field of approximately 3.3–3.5 MV/cm, more than ten times silicon’s ~0.3 MV/cm. That higher critical field strength drives several structural advantages:

- A GaN layer can be ~10–11× thinner than silicon for the same blocking voltage

- The thinner layer has lower resistivity, reducing RDS(on)

- A smaller die size results in lower parasitic capacitance

- Lower capacitance directly reduces switching losses

The system-level result is the ability to switch efficiently at frequencies well above 1 MHz, enabling smaller magnetics and higher-power-density designs.

GaN vs. Silicon: Body Diode

The second major structural advantage is the absence of a body diode. In a silicon MOSFET:

- Reverse current flows through the intrinsic body diode

- The diode stores the reverse recovery charge (Qrr)The diode stores the reverse recovery charge (Qrr)

- That charge must be removed on every switching cycle

- The energy is dissipated as heat

At high frequency, Qrr becomes a primary switching loss mechanism. In contrast, e-mode GaN:At high frequency, Qrr becomes a primary switching loss mechanism. In contrast, e-mode GaN:

- Has zero Qrr

- Does not rely on a body diode

- Exhibits very low gate and output charge due to its lateral structure

This eliminates reverse recovery losses entirely and makes GaN particularly well suited for hard-switching topologies, including:

- Half-bridges

- Totem-pole power factor correction (PFC)

In these architectures, reverse recovery losses define the efficiency ceiling for silicon, but not for GaN.

| Parameter | Silicon (Si) | Gallium Nitride (GaN) | Practical Impact |

| Bandgap Energy (Eg) | 1.12 eV | 3.4 eV | Higher critical field; better high-temperature stability. |

| Critical Electric Field | ~0.3 MV/cm | ~3.3–3.5 MV/cm | Smaller die for the same blocking voltage; lower parasitics. |

| Electron Mobility (µ) | ~1,400 cm²/Vs | ~2,000 cm²/Vs (2DEG) | Lower RDS(on) for reduced conduction losses. |

| Reverse Recovery Charge (Qrr) | High (nC to µC) | 0 | Eliminates a primary switching loss mechanism. |

| Max Gate Voltage | ±20 V | −5 V to +6 V (e-mode) / ±20 V (cascode) | E-mode requires a precision gate driver; cascode does not. |

Where GaN Power Devices Are Used

GaN’s physical advantages reduce the energy stored per switching cycle proportionally with frequency. Switch faster, and your magnetics (transformers, inductors, filters) shrink accordingly. That’s the system-level payoff.

Fast Chargers and Consumer Adapters

Consumer electronics were GaN’s proving ground. Fast chargers have been among the earliest adopters, driving volume growth and ecosystem maturity. Today, 65 W to 140 W GaN-based USB-C adapters fit in a fraction of the volume of their silicon predecessors because MHz-range switching frequencies allow the passive filter components to be dramatically smaller.

Data Centers

Server racks require maximum compute density with minimal power overhead. The industry’s shift from 12 V to 48 V rack backplanes requires highly efficient point-of-load step-down conversion at the board level. GaN-based LLC resonant converters and switched-capacitor topologies shrink power supply modules while cutting switching losses, thereby reducing the thermal load on facility HVAC and lowering the data center’s power usage effectiveness (PUE) ratio. Key emerging applications include AI data centers, which have enormous demands for high-speed computing and power.

Electric Vehicles and Renewables

Automotive drivetrains use GaN for high-efficiency on-board chargers (OBCs) and DC-DC converters. In solar energy, GaN microinverters offer higher conversion efficiency than silicon IGBTs, maximizing photovoltaic harvest while reducing inverter size and weight. The automotive segment is currently the fastest-growing end market for GaN devices, with a CAGR exceeding 37.5% through 2032.

PCB Design for GaN: What Changes, and What Breaks If You Ignore It

Designing a PCB for GaN is not simply a matter of swapping in a faster transistor. GaN transitions are exceptionally fast, with voltage slew rates (dv/dt) exceeding 100 V/ns and current slew rates (di/dt) ranging from 2 to 20 A/ns. Those edge rates will excite every parasitic inductance in your layout. The design rules below are not optional.

Gate Driving

The threshold voltage VGS(th) of an e-mode GaN HEMT is very low, typically 1 to 2 V. This makes it sensitive to unintended switch-on in high dv/dt applications. Gate drive design is demanding due to the low VGS margin, and the gate-source driving signal must be clean, with no overvoltage or ringing exceeding the gate’s maximum ratings. Place the gate driver as physically close to the GaN transistor as possible to minimize gate-loop inductance (LG). Use a dedicated isolated gate driver with high common-mode transient immunity (CMTI) to prevent the high dv/dt at the switch node from coupling back into the primary control logic.

Dead-Time Optimization

GaN lacks a body diode. It conducts reverse current through the 2DEG channel when VGS = 0, but GaN’s reverse conduction voltage drop is higher than that of a silicon MOSFET body diode, inducing higher reverse conduction losses. Minimize dead time in your half-bridge timing. Excessive dead time forces prolonged freewheeling through this high-drop conduction path, negating the switching efficiency gains you chose GaN to achieve.

Layout and EMI Mitigation

Minimize the area of the high-frequency power-switching loop. Place the high-side and low-side GaN devices directly adjacent to the high-frequency decoupling capacitors. Route the power loop on the top layer, and place a continuous solid ground-return plane on the adjacent inner layer. This cancels parasitic inductance by maximizing mutual coupling between the forward and return current paths.

Thermal Management

GaN generates less total heat than silicon at equivalent power levels, but that heat is concentrated in a much smaller die area, creating extreme localized thermal density. For surface-mount packages, use thermal vias directly beneath the thermal pad to conduct heat to a bottom-side heatsink or copper pour. Keep those vias dedicated to heat conduction, routing electrical current through them adds resistive heating and undermines their cooling function.

GaN PCB Design Checklist

Market Trajectory and What’s Coming Next

The power GaN device market is expanding rapidly, with a projected 42% CAGR, growing from approximately $355 million in 2024 to roughly $3 billion by 2030, according to Yole Group. While exact projections vary across analyst firms, the directional consensus is clear: GaN represents one of the fastest-growing segments in power semiconductors.

Automotive as the Primary Growth Driver

The automotive sector is currently the strongest growth vector. EV manufacturers are pushing for:

- Longer driving range

- Faster charging

- Higher overall system efficiency

At the same time, the industry is transitioning toward 800 V bus architectures. At these voltage levels, wide-bandgap efficiency advantages are amplified at every switching event. This shift is moving GaN into:

- Higher-power applications

- Automotive-grade reliability requirements

- Design spaces traditionally dominated by silicon IGBTs

Manufacturing Scale and Cost Reduction

On the production side, the cost trajectory is increasingly favorable.

- The dominant process today is 6-inch GaN-on-Si

- 8-inch GaN-on-Si manufacturing is gaining traction

- An 8-inch wafer yields roughly 80% more devices than a 6-inch wafer

That higher device density directly reduces cost per device. As a result, the historical price premium over mature silicon MOSFETs is narrowing, removing one of the primary barriers to adoption in cost-sensitive applications.

The Remaining Constraint: Execution

The limiting factor for GaN adoption is no longer materials physics. It is an engineering discipline. Designers must properly manage:

- Gate drive margins

- High dv/dt layout constraints

- Dead-time optimization

- EMI containment

When these requirements are respected, GaN becomes a straightforward performance upgrade. When treated as a drop-in silicon replacement, it can be unforgiving.

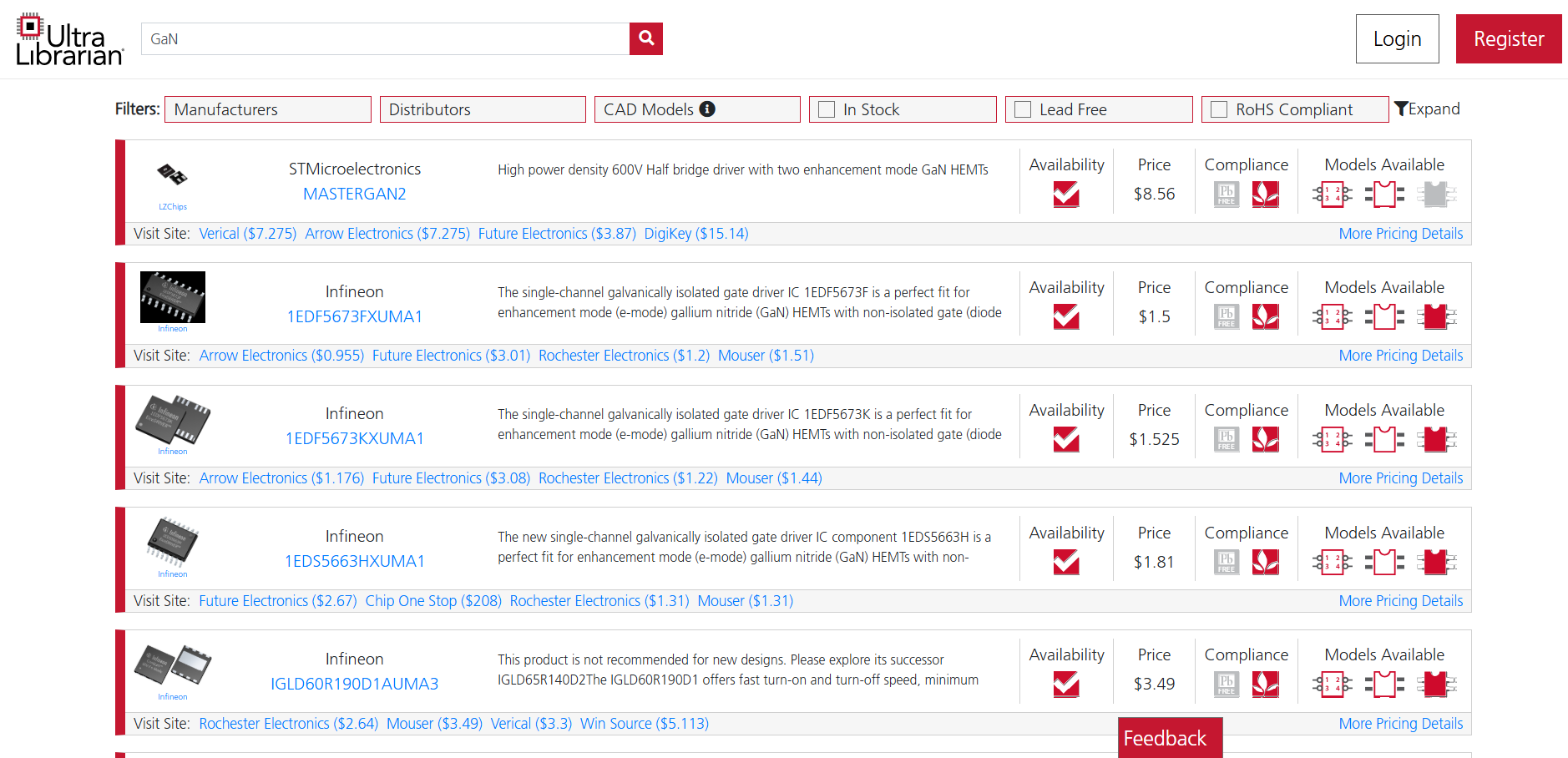

The transition to GaN power devices requires strict engineering discipline, but sourcing the right components shouldn’t be a bottleneck. Ultra Librarian provides verified CAD models for popular ECAD applications and connects you directly to worldwide distributors. Start building your next-generation high-efficiency power supply by finding the exact footprints and symbols you need today.

Working with Ultra Librarian sets your team up for success, ensuring streamlined and error-free design, production, and sourcing. Register today for free.